Die aktuelle Seite wurde 27239 mal besucht.

Besucher heute: 1

Zugriffe auf alle Seiten: 9422796

Server-Zeit: 01:51

19.07.2025

|

Das ppQBox-Mainboard

21.03.1999

Am Samstag, den 13.03.1999, habe ich das ppQBox Mainboard fertiggestellt. Jetzt (21.03.1999) habe ich die nötige Zeit gefunden, um die QBox-Sektion zu aktualisieren und Ihnen die Ergebnisse zu zeigen. Ich wählte den Namen "ppQBox" (pre_pre_QBox), weil ich denke, daß es noch zweier weiterer Generationen des Mainboards bedarf, bevor ich in der Lage bin, die "alles-vernichtende Supermaschine" ;) - die echte QBox - zu entwickeln...

1. Bilder des Boards

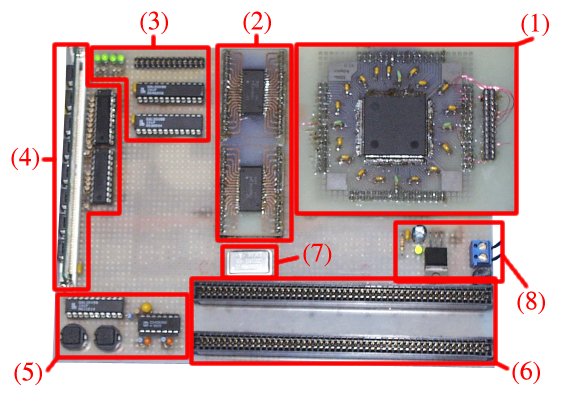

1.1 Oberansicht:

|

Dies ist die Oberansicht des ppQBox Mainboards. Ist es nicht ein schönes Board?!? ;)

Nun, wie Sie sehen können, besteht die QBox aus drei Boards: dem Mainboard, dem SRAM-Board und dem CPU-Board. Wenn ich die Möglichkeit erhalte, Multi-Layer-Boards zu fertigen, so wird es natürlich nur noch ein Board geben, aber leider habe ich keine Chance dazu.... :(

|

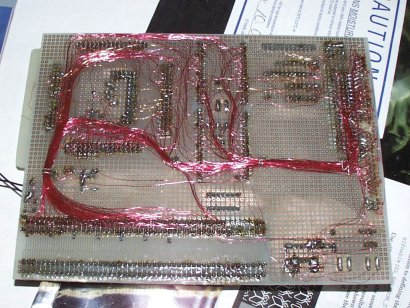

1.2 Unteransicht

|

Hehehe... und das ist die Unteransicht des Boards... verrückt, oder? ;) Hmm... Ich verwendete die unglaubliche Menge von 100 m Vero-Wire... nun, ich hatte viel Glück: Ich machte keinen Fehler und das Board arbeitete auf Anhieb!!! |

2. Funktionsblöcke des ppQBox Mainboards

- (1) CPU-Board bestückt mit einem XCF52064FT54 und BDM Debug-Verbinder

- (2) High-speed SRAM, mit GoldCap Spannungspuffer unterhalb des SRAM-Boards

- (3) Schnelles paralleles Netzwerk-Interface, realisiert mit zwei GAL20V8, es gibt auch noch ein paar freie IO-Leitungen, welche die vier LEDs ansteuern und die Möglichkeit für zukünftige Erweiterungen bieten.

- (4) PS/2 DRAM, der Hauptspeicher - natürlich auch EDO-RAM >=60ns. Ich kann alle Größen von PS/2-RAM in diesem Slot einsetzen.

- (5) Reset-Logik, Reset-Knopf und ein momentan unbenutzter Signal-Knopf

- (6) Zwei Erweiterungsslots mit allen wichtigen Signalen für spätere Hardwarezusätze sind verfügbar. Wenn ich es einmal benötige, kann ich in einen der beiden Slots auch ein PCI-Interface stecken... ;)

- (7) 32MHz Quarz-Oszillator, frei wählbar zwischen 0Hz und 50MHz.

- (8) +5V Stromversorgung (die 3,3V-Versorgung ist unter dem CPU-Board!)

3. Diskussion / Erklärung

Das ppQBox-Mainboard ist mehr oder weniger ein Standard-ColdFire-Design, es ist nicht viel eigene Logik darauf integriert. Aber das ist nicht wirklich wichtig, der wichtigste Schritt war und ist, ein eigenes Mainboard zu haben - kein weiterer Bedarf für das Motorola Entwicklerboard. Der Grund hierfür ist, daß ich auf diese Weise absolute Kontrolle/vollständiges Wissen über diese CPU auch aus Hardwaresicht habe. Das Motorola Entwicklerboard ist großartig, um die ersten Schritte mit der ColdFire-Architektur zu machen weil alles sofort einwandfei funktioniert. Aber wenn man (wie ich) ein eigenes Computersystem entwerfen will, sollte man nicht auf ein fertiges Beispiel-Design setzen...

Der Hautpvorteil meines Mainboard-Designs ist der ColdCap-gepufferte SRAM. Diese Option gibt mir die Möglichkeit, das System-BIOS in einen Speicher zu laden, der keine speziellen Programmieralgorithmen wie z.B. FlashROM benötigt, weil mein Speicher ein einfacher SRAM ist, welcher die Daten im ausgeschaltetem Zustand beibehält, indem die Versorgungsspannung mit einem 1 F GoldCap gepuffert wird.

Die beiden Erweiterungsslots, die auf dem Mainboard angebracht sind, verfügen über alle Signale des Adreß-Busses, Daten-Busses und der übrigen Steuersignale des ColdFire/Boards. Deswegen erlauben mir die beiden Slots, beinahe alles mögliche an das Board anzuschließen.

Beim Einschalten passiert folgendes:

- Der GAL mit der Reset-Logik (siehe (5)!) löst einen Master-Reset aus, um das komplette Board einschließlich des ColdFires zurücksetzen.

- Das globale Chip-select-Signal /CS0 wird immer von der CPU aktiviert, wenn ein Zugriff auf eine externe Adresse stattfindet.

Der SRAM ist mit /CS0 verbunden, so daß der ColdFire die ersten 8 Bytes Daten (Offset $00000000) von RAM liest.

Diese beiden Langworte sind der initiale Stack-Pointer und der initiale Programm-Counter, der ColdFire belädt die zugehörigen Register mit den gelesenen Werten.

- Nun fährt der ColdFire mit der Programmausführung beim neuen Programm-Counter fort. Das Programm an dieser Position ist eine Art BIOS, welches alles für ein vollständig funktionierendes System konfiguriert. Zunächst initialisiert es den DRAM-Controller, um den PS/2-DRAM zu aktivieren, als nächsten programmiert es /CS1 auf die Netzwerk-GALs, anschließend programmiert es /CS0 auf eine neue Position.

- Nun ist das System "gebootet" und die BIOS-Routine veranlaßt die CPU, ein Benutzerprogramm zu starten.

Nun werden Sie sich fragen: "Wie bekommst Du den Code (BIOS) in das unprogrammierte Board??" -- Nun, das ist wirklich einfach: Ich verwende ein BDM-Debug Interface-Kabel, verbunden mit meinen PC, womit ich alles für ein erstes Setup initialisieren kann. Dieses Setup ist im Grunde genommen nur einmal notwendig, weil die nächsten Einschaltvorgänge vollständing (ohne einen PC zu benötigen!!) vom BIOS in den GoldCap-gepufferten SRAMs gesteuert werden... ;)

Hmm... das ist zunächst alles.

Kommentare oder Fragen? Schreiben Sie mir einfach eine E-Mail... :)

|

|